Formada per 14 grups de recerca i coordinada per l’IMB-CNM del CSIC, estimularà la investigació, la formació i la cooperació amb empreses en l’àmbit del hardware obert. La UAB en forma part i acull les jornades de presentació els dies 5 i 6 de febrer a l’Escola d’Enginyeria.

La Xarxa-RISCV neix com a xarxa d’investigació al voltant de les arquitectures de maquinari obert basades en l’ISA RISCV (el llenguatge màquina de codi obert), però pretén anar més enllà i generar sinergies col·laboratives entre els àmbits de la recerca, la formació i la innovació.

Està formada per 14 centres de recerca i universitats, i compta amb el suport inicial del Ministeri d’Innovació i Ciència. Coordinada per l’Institut de Microelectrònica de Barcelona (IMB-CNM) del Consell Superior d’Investigacions Científiques (CSIC), agrupa 14 equips de diferents centres de recerca: Barcelona Supercomputing Center – Centre Nacional de Supercomputació (M. Valero); Centre Nacional de Microelectrònica del CSIC (Ll. Terés); Universitat Autònoma de Barcelona (A. Espinosa), Universitat de Barcelona (M. López), Universitat de Cantàbria (E. Vallejo), Universitat Complutense de Madrid (K. Olcoz), Universitat de La Corunya (R. Doallo), Universitat de Extremadura (J. Plaza), Universitat de les Illes Balears (B. Alorda), Universitat de Múrcia (A. Ros), Universitat Politècnica de Catalunya (F. Moll), Universitat Politècnica de València (J. Flich), Universitat Rovira i Virgili (O. Farràs) i Universitat de Saragossa (V. Viñals). A més, compta ja amb més de 25 empreses interessades a participar en les seves activitats.

Els dies 5 i 6 de febrer es realitzen les primeres Jornades d’aquesta xarxa a l’Escola d’Enginyeria (Carrer de les Sitges), al campus de la Universitat Autònoma de Barcelona, jornades que suposaran la seva presentació en societat. Les jornades de la Xarxa-RISCV es combinaran i coordinaran amb les jornades de la xarxa CAPAP-H que es realitzaran a l’Escola d’Enginyeria de la UAB els dies 6 i 7 febrer.

Reduir la dependència de l’oligopoli del mercat de processadors

L’arquitectura RISC-V d’ISA obert es va començar a forjar el 2010 a la Universitat de Berkeley com una necessitat per reduir l’enorme i creixent complexitat dels repertoris d’instruccions dels microprocessadors, i per limitar la forta dependència de tercers països i oligopolis empresarials.

Els microprocessadors són el cor de tots els dispositius electrònics amb capacitat de còmput. Contenen el repertori d’instruccions bàsiques (ISA, de l’anglès Instruction Set Architecture) del que cada màquina pot executar. Aquest paquet d’instruccions en llenguatge màquina és la peça indispensable per al funcionament del dispositiu i és també el punt de trobada de hardware i software.

El mercat actual dels microprocessadors està dominat per tot just tres grans fabricants (INTEL, ARM, AMD), cada un amb el seu propi ISA i amb diferents models de negoci. En el cas de l’arquitectura x86 (INTEL i AMD) el principal inconvenient és que l’ISA està poc optimitzat per la necessària compatibilitat amb les generacions anteriors. A més, en les seves últimes versions cal compensar amb regalies a INTEL i AMD. El model de negoci d’ARM és el d’un ISA tancat. Per tant, hi ha l’obligació de pagar quantitats que van des dels centenars de milers fins als milions d’euros.

L’arquitectura RISC-V d’ISA obert persegueix reduir aquesta creixent complexitat dels repertoris d’instruccions que dominen el mercat, que són principalment dos, Intel x86 i ARM. L’objectiu és fixar un ISA reduït, estàndard, modular i obert que pugui tenir extensions per àmbits d’aplicació específica, i eviti o limiti els sobre-costos per regalies i desenvolupament.

El maquinari de codi obert té el potencial de ser tan disruptiu com ho va ser Linux, paradigma del programari de codi obert, que va facilitar el creixement d’una enorme comunitat de desenvolupament de programes en obert i va aconseguir reduir la dependència dels usuaris respecte a les grans firmes de programari.

«Les noves arquitectures RISC-V d’ISA obert ofereixen una oportunitat per guanyar en independència tecnològica, augmentar les garanties d’un hardware més robust i segur, reduir els riscos de monopoli i facilitar la competència de mercat, cosa que Europa no pot desaprofitar», comenta Lluís Terés, investigador del CSIC a l’IMB-CNM i coordinador de la xarxa RISCV.

Recerca, formació i innovació industrial

La Xarxa-RISCV promourà la col·laboració i l’evolució conjunta de la investigació, la formació i la innovació.

En investigació s’obren noves perspectives al disposar d’un ISA obert com a estàndard de base i es proposen crear extensions especialitzades en diferents camps, com la criptografia, la genòmica, la intel·ligència artificial o la internet de les coses. Al seu torn, aquests nous mercats oberts tindran noves necessitats i reptes que l’R+D+I acadèmica haurà d’afrontar i resoldre juntament amb la indústria.

A nivell formatiu, tant universitari com professional, RISC-V ofereix una oportunitat per renovar i reorientar els currículums acadèmics, i permetrà abordar aquesta nova arquitectura anticipadament, ja que encara no ha explotat al mercat, donant noves competències i avantatges competitius als titulats. Així mateix, la indústria podrà tenir una participació més activa en els processos formatius.

Pel que fa a la prospectiva i innovació industrial, RISC-V és una aposta de futur per a empreses tecnològiques de tot tipus i grandària, ja que podran abordar el desenvolupament dels seus propis nuclis processadors o seleccionar de diferents proveïdors el RISC-V més adequat a les seves necessitats, sense haver d’afrontar alts costos per regalies.

«En els tres àmbits esmentats, la incorporació del hardware obert facilita i promou l’actitud i l’activitat col·laborativa», explica Mateo Valero, director del BSC. «Per tant, considerem que la major contribució de RISC-V consistirà en facilitar un entorn de sinergies col·laboratives entre aquests tres actors fonamentals, investigació, formació i prospectiva industrial».

Lagarto, un embrió que neix juntament amb la Xarxa-RISCV

La Xarxa-RISCV es va gestar juntament amb el desenvolupament de Lagarto, el primer processador amb repertori d’instruccions ISA RISCV de codi obert desenvolupat a Espanya. Aquest projecte, liderat pel Barcelona Supercomputing Center (BSC), va comptar amb la participació de l’IMB-CNM del CSIC, del Centre de Recerca en Computació de l’IPN mexicà, i dels Departaments d’Arquitectura de Computadors (DAC) i d’Enginyeria Electrònica de la UPC. Lagarto es va crear a partir d’un disseny inicial de l’IPN mexicà.

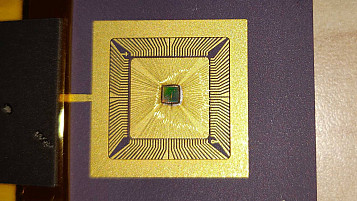

El sistema, que ha donat uns resultats superiors als esperats, va ser desenvolupat totalment a Espanya i fabricat a Taiwan amb la tecnologia de TSMC CMOS de 65 nanòmetres a través dels serveis d’EUROPRACTICE, una plataforma creada per la Comissió Europea per impulsar el desenvolupament de sistemes integrats intel·ligents amb tecnologies microelectròniques.

La fita de Lagarto és que està desenvolupat en base a un ISA obert en la seva totalitat i, sobretot, que és el primer processador de codi obert creat a Espanya, amb l’ambició de contribuir com un dels primers embrions dels futurs processadors europeus. Val a dir que el primer xip espanyol, que no era un processador, va ser dissenyat el 1982 a la UAB (Grup VLSI) per alguns investigadors del mateix equip que ara, des de l’Institut de Microelectrònica de Barcelona (IMB-CNM) del CSIC, han contribuït al desenvolupament del Lagarto RISC-V.

En tot cas, el desenvolupament de processadors mai havia anat més enllà dels models sobre

paper o de laboratori i sense projecció de mercat.

«Un xip, o un ASIC (Application Specific Integrated Circuit)», aclareix Lluís Terés, «fa una funció concreta i més o menys tancada. No és així el processador, que es pot programar amb software des de l’exterior, pot fer coses molt diferents i és el nucli de qualsevol dispositiu amb capacitat de computació ».

El Laboratori Europeu per a l’Arquitectura Oberta (LOCA)

Una altra iniciativa, en consonància amb la Xarxa-RISCV, és la creació de l’European Laboratory for Open Computer Architecture (LOCA), liderada pel BSC i que tindrà seu a Barcelona. La seva missió serà dissenyar i desenvolupar a Europa xips i processadors de computació d’altes prestacions.

»LOCA serà un laboratori col·laboratiu que acollirà empreses, fundacions i institucions acadèmiques que comparteixen la visió que cal crear arquitectures obertes per garantir la transparència, la competitivitat i la sobirania tecnològica", afirma Mateo Valero, director del BSC.

El projecte DRAC

El projecte DRAC (Designing RISC-V-based Accelerators for next generation Computers) és una iniciativa catalana liderada pel BSC, amb participació de quatre centres universitaris (UAB, UB, UPC i URV), diverses empreses (eSilicon, SemiDynamics, Silicon Gears ) i centres col·laboradors (CNAG, CNM-CSIC). L’equip de DRAC està començant a treballar en el desenvolupament d’acceleradors de còmput per àmbits específics d’aplicació (seguretat, criptografia, genòmica, conducció automàtica, etc.), basats en l’arquitectura RISC-V. Es tracta d’un consorci local que aglutina l’experiència necessària per cobrir totes les etapes de desenvolupament d’un processador i que té la voluntat de contribuir a l’ecosistema local i internacional al voltant d’aquestes noves arquitectures obertes.

El projecte DRAC està coordinat per Miquel Moretó, del BSC i investigador Ramon y Cajal de la Universitat Politècnica de Catalunya (UPC), i està co-finançat per la Generalitat de Catalunya a través del programa «RIS3 CAT-Tecnologies Emergents» i el fons EU-ERDF de la Unió Europea.

La RISC-V Foundation

A nivell mundial, el moviment que impulsa l’arquitectura de hardware de codi obert va començar a agafar força el 2015 amb la creació de la RISC-V Foundation, que va publicar en obert les especificacions de base de l’ISA RISC-V i que s’ocupa de coordinar i mantenir l’evolució del corresponent estàndard de facto. Aquesta fundació ha crescut i segueix creixent dia a dia. Actualment, ja té més de 450 membres en 33 països de tot el món, dels quals més de 200 són del sector industrial amb petites, mitjanes i grans empreses tecnològiques.

Pàgina de les jornades:

http://red-riscv.org/

Les sessions tècniques seran retransmeses en “streaming”